- 您现在的位置:买卖IC网 > Sheet目录1992 > DAC5674IPHPG4 (Texas Instruments)IC DAC 14BIT 400MSPS 48-HTQFP

DAC5674

SLWS148A SEPTEMBER 2003 REVISED OCTOBER 2005

www.ti.com

5

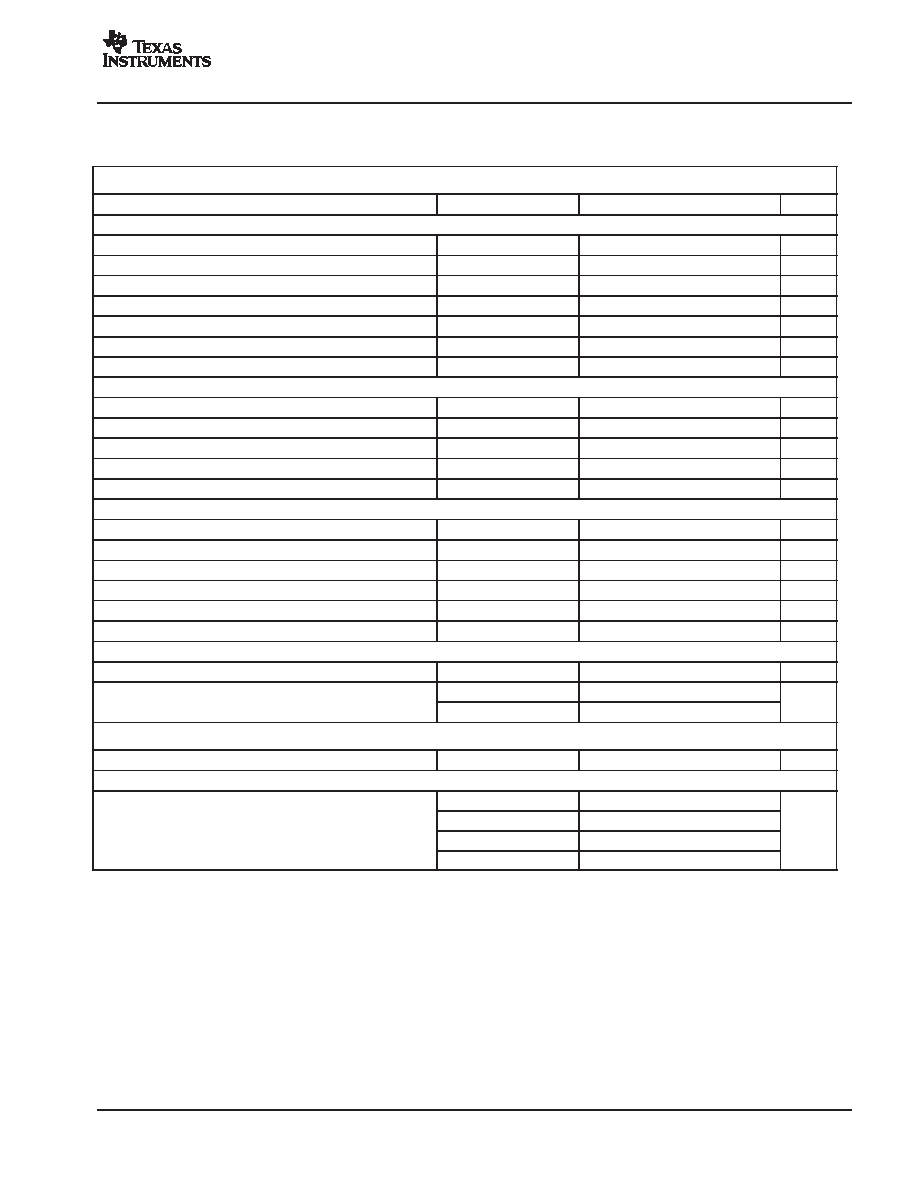

ELECTRICAL CHARACTERISTICS

over recommended operating free-air temperature range, AVDD = 3.3 V, CLKVDD = 3.3 V, PLLVDD = 3.3 V, IOVDD = 3.3 V, DVDD = 1.8 V,

IOUTFS = 20 mA, differential transformer coupled output, 50-

doubly terminated load (unless otherwise noted)

DIGITAL SPECIFICATIONS

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

CMOS INTERFACE

VIH

High-level input voltage for SLEEP and EXTLO

0.7 AVDD

V

VIL

Low-level input voltage for SLEEP and EXTLO

0

0.3 AVDD

V

VIH

High-level input voltage other digital inputs

0.7 IOVDD

V

VIL

Low-level input voltage other digital inputs

0

0.3 IOVDD

V

IIH

High-level input current

10

30

A

IIL

Low-level input current

1

10

A

Input capacitance

1

5

pF

TIMING INTERNAL CLOCK MODE

tSU

Input setup time

0.6

ns

tH

Input hold time

0.6

ns

tLPH

Input latch pulse high time

2

ns

tlat_2x

Data in to DAC out latency 2

× interpolation

26

clk

tlat_4x

Data in to DAC out latency 4

× interpolation

35

clk

TIMING EXTERNAL CLOCK MODE

tsu

Input setup time

5

ns

th

Input hold time

1.75

ns

tlph

Input latch pulse high time

2

ns

td_clk

Clock delay time

3.6

ns

tlat_2x

Data in to DAC out latency 2

× interpolation

26

clk

tlat_4x

Data in to DAC out latency 4

× interpolation

35

clk

PLL

Input data rate supported

5

200

MSPS

Phase noise

At 600-kHz offset

124

dBc/Hz

Phase noise

At 6-MHz offset

134

dBc/Hz

DIGITAL FILTER SPECIFICATIONS

fDATA

Input data rate

200

MSPS

FIR1 and FIR2 DIGITAL FILTER CHARACTERISTICS

0.005 db

0.407

Pass-band width

0.01 dB

0.41

fOUT/

Pass-band width

0.1 dB

0.427

fOUT/

fDATA

3 dB

0.481

fDATA

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DAC7621EBG4

IC SNGL 12BIT PARALLEL D/A 20SSO

DAC7801KPG4

IC DUAL 12BIT CMOS DAC 24-DIP

DAC8043AESZ

IC DAC 12BIT MULT SRL INP 8SOIC

DAC8043GP

IC DAC 12BIT MULTIPLY CMOS 8-DIP

DAC8221GP

IC DAC 12BIT DUAL W/BUFF 24-DIP

DAC8222GPZ

IC DAC 12BIT DUAL W/BUFF 24DIP

DAC8229FSZ-REEL

IC DAC 8BIT DUAL V-OUT 20SOIC

DAC8248FS

IC DAC 12BIT DUAL W/BUFF 24-SOIC

相关代理商/技术参数

DAC5674IPHP-ND

制造商: 功能描述: 制造商:undefined 功能描述:

DAC5674IPHPR

功能描述:数模转换器- DAC 14-Bit 400 CommsDAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

DAC5674IPHPRG4

功能描述:数模转换器- DAC 14-Bit 400 CommsDAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

DAC5675

制造商:TI 制造商全称:Texas Instruments 功能描述:14-BIT, 400-MSPS DIGITAL-TO-ANALOG CONVERTER

DAC5675A

制造商:TI 制造商全称:Texas Instruments 功能描述:14-Bit, 400MSPS Digital-to-Analog Converter

DAC5675AEVM

功能描述:数据转换 IC 开发工具 DAC5675A Eval Mod RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V

DAC5675AIPHP

功能描述:数模转换器- DAC 14-Bit 400-MSPS RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

DAC5675AIPHP

制造商:Texas Instruments 功能描述:IC DAC 14BIT 400MSPS 48-HTQFP